발행하는 글은 설계독학 유튜브에 사용할 자료로 사용예정입니다.

글의 저작권은 맛있는비빔밥 에게 있습니다.

설계독학 유튜브 입니다.

Intro

안녕하세요. 설계독학의 맛비입니다. Xilinx FPGA 를 공부하기 위한 첫걸음 입니다.

Tool 버전이 다르더라도 설치과정은 거의 유사하리라 생각이 들어요.

따라만 하시면 성공적으로 설치 하실 수 있을꺼에요.

원래는 1월 23일에 올리려고 했는데, 몇몇 분들이 Tool 설치에 대해 여쭤보시는 경우가 있어서, FPGA 를 진행하기 위한 Tool 설치 영상을 미리 올리게 되었습니다.

FPGA 는 2021년 3월 부터 시작입니다. :)

오늘은 Vitis 와 Vivado 를 설치하는 시간을 가지려고 합니다.

예전에 Verilog HDL 을 배울때는 Linux 환경에서 진행을 했었어요.

그런데 이번 FPGA 편은 Window 에서 진행을 하려고 합니다.

이유는 첫번째로, 성능에 들 수 있습니다.

WSL 환경 자체가 전체 PC 의 Full Performance 를 낼 수 없어요.

FPGA 에서 하나의 bit stream 을 만들기 까지 많은 과정이 필요한데, 그말은 PC 의 CPU 성능에 따라서 결과가 나오는 시간이 결정이 됩니다.

WSL 에서 build 를 하게되면 너무 오래걸리더라구요.

그래서 Verilog HDL 의 simulator 는 linux 환경에서 진행할 생각이구요.

FPGA 를 공부할때는 Window 에서 진행할 생각입니다.

WSL 이 아닌, 진짜 Linux 를 사용하고 계시다면 굳이 한번더 설치할 필요가 있을까? 생각은 들어요.

GUI 환경에서 공부를 할 것이기 때문에, Window 와 큰 차이는 없을꺼에요.

단지, 리눅스에는 디바이스 드라이버 를 알아서 잘 잡아주셔야 한다가 큰 차이입니다.

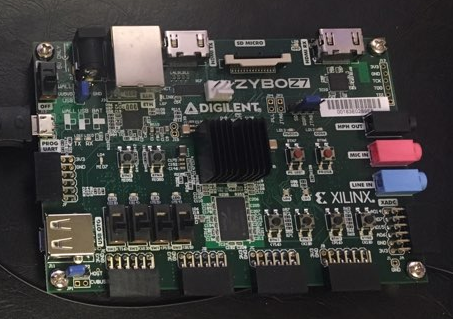

두번째 이유는 앞서 말한 디바이스 드라이버 이슈입니다. 사용하는 Zybo board 에는 Jtag 이 USB 로 달려있습니다.

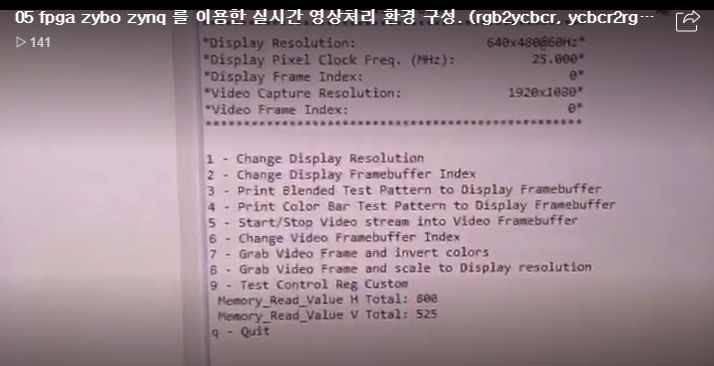

JTAG 이 무엇인지 간단하게 설명드리면, 여러분이 빌드한 image 파일을 FPGA 에 write 할 때 사용할 수 있구요.

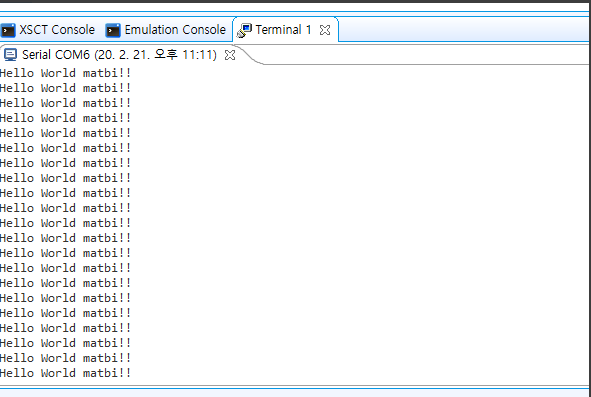

Debugging 할때도 이 JTAG 을 통해서 합니다. 그래서 개발할 때 필수로 잡아줘야 하는 환경이죠. 거기다 Zybo board 에는 UART 까지 사용이 가능해요.

UART 는 많이 들어보셨을 텐데, Zybo board 에서의 UART 는 대부분 어떤 역할로 사용하냐면, User 가 terminal 에서 zybo board 의 상태를 print 해주기 위해서 사용한다.

UART 를 통해서 상태를 Print 찍고, 그리고 User 가 직접 입력을 넣어 줄 수도 있어요.

해서 이런 기능을 사용하려면, Linux 상에서는 디바이스를 정확하게 잡아주셔야되는데, 이걸 잡기가 처음 배우시는 분들은 어려울 수 있습니다.

권한이라던가 여러가지 이슈들이 있고, 이를 매번 댓글에 질문으로 올라올 확률이 매우 크다 생각이 들어요.

해서 여러분들이 편해 하시는 Window 에서 진행하려고 합니다. 환경 문제로 여러분들의 발목을 잡지 말자가 가장 큰 이유에요.

설치 내용은 동영상을 참고해주세요 :)

마무리

오늘 내용은

- Vitis 를 windows 에 설치했습니다.

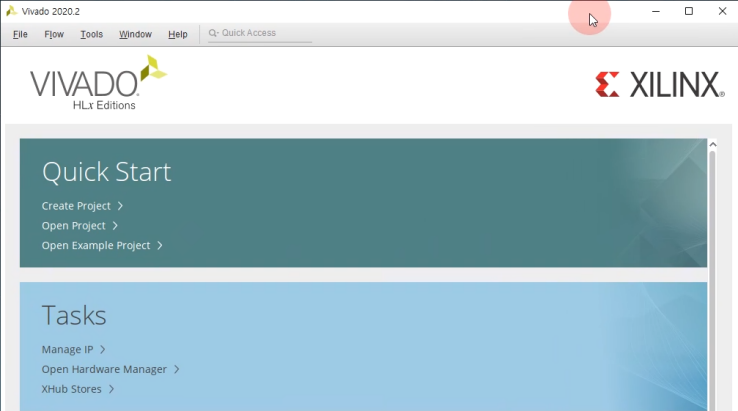

- 설치 후에 Vitis 와 Vivado 실행을 확인했습니다.

- Zybo Z7 board 의 board 파일을 다운로드 받았고 설치했습니다.

다소 길었는데, 한번만 하시면 되요. 여기까지 하셨으면 설치시간이 아까워서라도 공부하셔야 합니다.

고생하셨구요. 다음시간에는 우리가 사용할 (Zybo Zy 20) 보드에 대해 이야기 해볼께요.

다른 보드를 갖고 계시더라도 공통되는 내용이니까 들어주세요.

코로나 조심하시고 다음시간에 봬요 :)

'설계독학맛비 YouTube > 02 Xilinx FPGA' 카테고리의 다른 글

| Xilinx FPGA Reset Guide (0) | 2021.05.12 |

|---|---|

| [AI-Based Super Resolution HW IP] Deepfield-SR 을 소개합니다. (2) | 2021.01.26 |

| Matbi's Xilinx FPGA Syllabus (2) | 2021.01.06 |

| Xilinx FPGA 를 처음 공부할 때 봤으면 하는 글... (1) | 2020.12.16 |

| Zybo Z7 20 개봉. (정상동작 확인) (1) | 2020.12.12 |