개발 편의성을 위한 소소한 Tips/04 질의 응답 정리

Vivado on WSL 재설치 관련 질문

Q.안녕하세요.단순 재설치 관련 질문이어서 알려주신 포맷을 따르지 않고 질문드립니다.왕초보인데요.설치단계에서 강사님이 얘기하지 않은 명령어를 실수로 실행해 버리기도 하고(sudo apt upgrade -y), 에러도 발생해서 새로 설치하고 싶습니다.그래서 기존꺼를 지우고 재설치하는 방법에 대해 알려주시면 감사하겠습니다.그리고 추가 질문은 설치가 제대로 되면 몇G정도를 차지하는지요?감사합니다 1. 기존 환경 삭제(1) 기존 소프트웨어 및 관련 파일 삭제Vivado와 Vitis의 삭제: 설치된 경로(예: /tools/Xilinx 또는 /opt/Xilinx)를 삭제합니다. sudo rm -rf /tools/Xilinx sudo rm -rf /opt/Xilinx라이센스 관련 파일 삭제: 라이센스 파일 또는 설..

240514 라이브 방송 QnA

Q A 안녕하세요! 막연히 비메모리 반도체 설계 직무에 희망하는 학부생입니다.코딩을 할때 즐겁기도 하고 비메모리 반도체에 종사하고 싶다는 목표로 디지털 회로설계쪽으로 생각 중인데 제가 생각한 직무와 딱 맞는 직무는 찾기 힘드네요ㅜㅠ저는 코딩할 때 특히 디버깅을 통해 출력물의 오류를 살펴보며 코딩하는 것에서 제가 고친 코드의 영향으로 출력물이 즉각적으로 수정되어 확인하는 것에서 재미를 느꼈습니다. (ex) HDL을 이용한 시스템의 timing diagram, C언어 이미지처리)그런데 회사의 직무들을 살펴보니 HW, SW로 설계가 나뉘고 저는 이 중 어떤 것이 제가 흥미를 느낀 부분과 가까운지 열심히 찾아봤지만 아직 잘 모르겠어서 맛비님께 죄송하지만 질문을 드리게 되었습니다...!제 질문은 2가지 입니다...

[FPGA Q/A. 029] Vivado, Vitis 설계 내용 수정 후 프로그램 실행

Q Vivado, Vitis 설계 내용을 수정한 후 보드에 프로그램을 바로 올려서 확인하는 방법이 있는지 궁금합니다. 현재는 Block design을 수정하게 되면 아래 과정을 진행하여 보드에서 동작을 확인합니다. Synthesis, implementation, Generate Bitstream -> xsa file을 추출하여 Vitis에서 다시 Application project를 생성 -> Build Project, Run as hardware 이러한 과정을 모두 거치는 것이 시간이 너무 오래 걸립니다. 혹시 위 과정에서 설계 내용을 수정했을 때 하지 않아도 되는 과정이 있을까요?? 또는 추출한 xsa file을 Application Project를 생성하지 않고 바로 적용시키는 방법이 있을까요?? ..

[Verilog HDL Q/A. 028] 왜 F/F들은 clock의 posedge edge에만 동기화 되는거지? posedge 와 negedge 둘 다 동기화될 수도 있지 않을까? 속도도 2배 빠를 것이고, double edge F/F이 있는데?

Q 안녕하세요 맛비님. 맛비님 코드를 보던 도중에 왜 F/F들은 clock의 posedge edge에만 동기화 되는거지? posedge 와 negedge 둘 다 동기화될 수도 있지 않을까? 속도도 2배 빠를 것이고, double edge F/F이 있는데? 라는 의문이 들었습니다. 그래서 인터넷 서치를 하며 내린 결론은 다음과 같습니다. 할 수는 있다. 하지만 하게 된다면 Register와 Register 사이의 연산량이 절반으로 줄어들 것이고, timing violation이 생길 위험이 두배 증가한다. 대부분의 FPGA에는 양쪽 edge에 동작하는 F/F이 없다. 라고 생각했습니다. 혹시 이 부분에 있어서 틀린 점과, 맛비님께서 아시는 또 다른 이유 있는지 질문드립니다. 항상 감사합니다 :) A 안녕하..

HW 엔지니어가 알아두면 좋을 소소한 알쓸신잡

안녕하세요. 설계독학맛비입니다. 최근에 이것저것? 인터넷을 끄적이다가, Hardware Engineer 가 알아두면 좋은 내용들이 있어서 소개해 드립니다. 첫번째 이야기!! 이중 for 문에서 memory index 접근 방법에 따른 Performance 차이. (시간복잡도) 블라인드 앱에서 본 글인데요. 여러분들 맞출 수 있나요? (저도 어버버 할듯... ㅎㅎ) Q. 원문============= 인터뷰 보는데.. 시건복잡도 문제를 수기로 작성해주고 어떤게 더 빠른지 말해달라고 했었는데… 1. 이중 for문 (i -> j 순서) > sum += arr[i][j] 2. 이중 for문 (j -> i 순서) > sum += arr[i][j] 어떤게 더 빠른지 말하라고 했는데.. 혼이 씌었는지 1번이 더 빠르다..

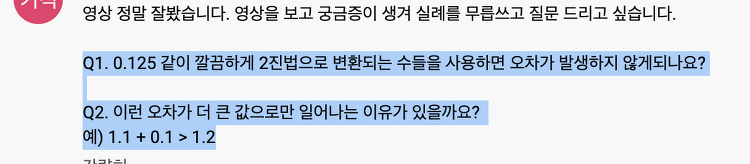

[Verilog HDL Q/A. 027] DDR, FIXED I/O 질문드립니다.

안녕하세요 맛비님!! 1. 다음 사진처럼, DDR, FIXED I/O, LED가 칩 외부의 보드 핀과 연결되는 것으로 알고 있는데, LED는 출력부분이니까 이해했습니다. 그런데 DDR은 Double Data Rate로, 클럭의 양쪽 엣지를 동기화하여 입력값을 받는다고 알고 있는데 쓰이는 이유가 궁금합니다. 그리고 FIXED I/O는 인터넷에서 찾아보니, Standard I/O 와 연관이 되어있고, Standard I/O 는 LVDS, LVCMOS 등등의 표준 규격으로 알고 있지만, FIXED I/O의 정확한 개념을 잘 모르겠습니다. (고정된 input output인가요?) 2. Vitis를 사용하지 않고, Vivado에서 바로 open hardware 후 program device를 하지 않는 이유가 궁..

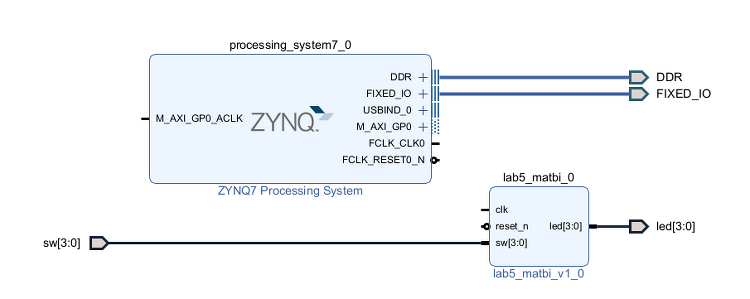

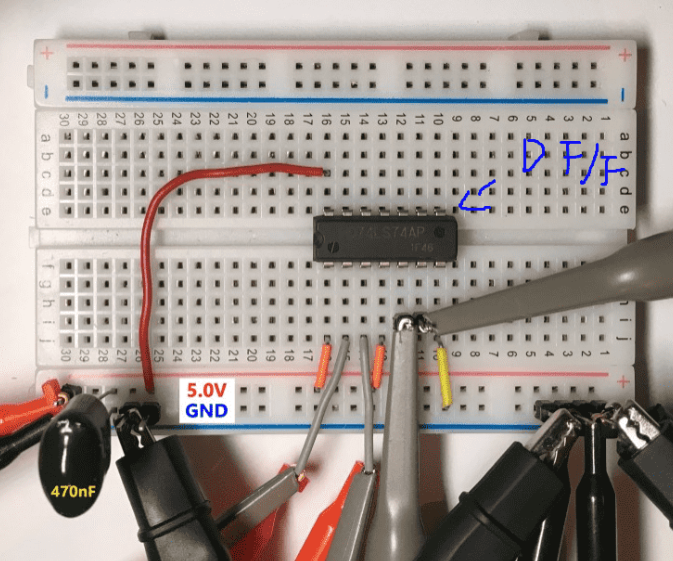

[Verilog HDL Q/A. 026] DTU와 testbench에 대해 제가 제대로 이해한건지 궁금하여 여쭤봅니다

Q 여기서 제가 뭔가 부족하게 이해하고 넘어간것같아서 여쭤봅니다만. DTU는 플립플롭 등의 설계모듈 testbench는 입력 및 결과측정용으로 이해하면 될까요? 예를들어 이렇게 있을 때 가운데 칩이 DTU라 하고 그 외의 선들과 연결되어있는것들(클록펄스 입력기, 데이터입력기(본 강의에선 클록펄스를 그대로 입력했네요), 출력된 데이터 인식기) 등 testbench로 이해하면 적절한가 싶어 여쭤봅니다. A 안녕하세요 :) Testbench 의 적절한 예시인 것 같습니다. HW 가 실제 Chip 혹은 FPGA 가 올라간다라고 가정하면, (HW == DUT) Testbench 는 실제 존재하는 HW 가 아닙니다. Testbench HW 검증을 위한 SW 입니다. Testbench = 빵판에 구성된 회로 (DUT..

[FPGA Q/A. 025] timing violation

Q 안녕하세요, 강의 잘 보고 있습니다. synthesis 끝난 후에 타이밍 데이터들이 report 되는데, 맛비님께서 타이밍 이슈가 없다고 말씀하셨습니다. 그 이유가 TNS, THS가 0이기 때문인건가요? 만약 맞다면 1n만큼의 TNS가 생기면 timing violation이 생겼다고 보면 될까요? 감사합니다. A 안녕하세요 :) Timing violation 은 Targeting 하는 frequency 를 met 하지 못하면 발생하게 됩니다. 예를들어 Target frequncy 를 100MHz 로 하고, 이는 10ns 입니다. FPGA 에 동작을 위해서는 Register to Register 사이의 Setup 과 hold time 이 10ns 안에 들어와야합니다. (setup, hold time 은..