설계독학맛비 YouTube

240308 라이브 방송 QnA

Q A 이쪽 분야도 풀스텍이 가능한가요 아 경험이 가능한가 에 대한 질문이였습니다 다 한다는건 아닙니다. (반도체 업계의) 풀스텍 스펙정의 설계 PI PD 혼자 할 수 있는 일은 아닌데, 한 명의 천재 (풀스택 전문가) 가 다수를 먹여살릴 수 있는 분야. 가능해요. 아날로그 에서 디지털로 갈수있나요 갈 수 있다. 다만, 아날로그 경력이 너무 높으면, 디지털로 굳이..? 안녕하세요 요즘 경기상황이 어떤가요?? 올해 신입채용이 쫌 있을까요? 어느 뉴스 기사에 삼성 공채 1만명 뜬다고 하더라구요 디지털회로 파운드리쪽은 경력직 많이 뽑더라구요 신입 잘 모르겠는데.. 항상 이야기 하지만, 국내의 (제대로 된) 설계 인력은 부족하다. 개인적으로 반도체 분야 취업은 항상 좋아요. (신입 or 경력) → (제대로 된)..

240128 라이브 방송 QnA

Q A 올해 3학년 되는데 회설갈지 반도체공정 갈지 고민입니다 ㅠㅠ 사실 회설 가고픈데 담당 교수님이 1분이라서요.. 컴구조설계와 Soc설계까지 과목을 하시는 분이 1명인데, 학부연구실도 가기 힘들고, 대학원은 운영 안하셔서 거기 속해있는 학부연구생들을 이기기 힘들거 같고, 차라리 전공공부해서 학점 잘 챙기고 gsat잘봐서 삼성공정라인으로 갈지 고민이네요.. 회설이 쫌 메인?부서 같은 이미지가 있어서 가고픈데, 이도저도 아니면 학점 잘챙겨서 공정 갈지 고민입니다 ㅠ 현재 대학도 서울에서 유명한 대학인데 회설 인프라가 약하네요... 올해 23살인데 재수해서 sky라인 공대 노려볼까 하는데, 그러면 30살에 가까이에 학사졸업일텐데, 너무 늦은거 같네요.. 재수도 한방에 된다는 보장도 없고, 학벌도 높일겸 ..

[Verilog HDL/FPGA 외전1 - 시계만들기] 예고편

설계독학만의 노하우가 담겨있는 강의로 잠깐? 찾아왔습니다. Verilog HDL 시계만들기 강의를 추가하였고요. 같이 공부해보아요. https://inf.run/Ma3a 안녕하세요. 설계독학의 맛비입니다. 외전으로 맛비 watch를 만들어보는 시간을 준비했습니다. 흔히 Verilog HDL 과제로 시계만들기를 많이 하시더라고요. 이 시계만들기는, 개인적으로 굉장히 좋은 과제다 라고 생각합니다. 이 과제를 수행하려면, Clock, Sequential/Combinational logic 의 이해, counter 설계, Testbench 검증환경, 거기다가 FPGA 에 올려보는 과정까지, 정말 여러분들이 현업에서 꼭 필요한 모든 경험을 해보실 수 있어요. 다만 이제는 학생분들이 더 똑똑해 지셔서, 시계만들기 ..

[공지] [설계독학공지]멘토링 Open 반도체 회로설계 엔지니어 취업 / 이직 / 커리어 상담

인프런의 멘토링 기능을 Open 했습니다. 이제까지 여러분들에게 상담형식의 질의응답은 유튜브 라이브를 통해서만 했었는데요. 이제는 인프런의 “멘토링” 기능을 통해서. 정식으로 여러분들과 1:1로 이야기를 해보려고 합니다. 멘토링은 하단의 링크를 통해서 바로 접속이 가능합니다. [설계독학맛비] 멘토링 - 선배와 동료들에게 조언을 구해보세요. | 인프런 개발자, 디자이너, 기획자, IT 업계 선배와 동료들에게 조언을 구해보세요. 더 빨리, 멀리 갈 수 있어요. 😀 www.inflearn.com 🙋♂️소개 안녕하세요. 👋 설계독학 맛비입니다. 저는 현재 비메모리 반도체 설계 외국계 회사에 재직중인 13년차 엔지니어 입니다. 대기업, 중소기업, 스타트업, 외국계 까지 모두 경험해 보았습니다. Team lead..

비메모리 설계 엔지니어를 위한 설계독학맛비's 로드맵 (부제 : 내가 과거로 돌아간다면...)

안녕하세요. 설계독학의 맛비입니다. 많은 분들이 비메모리 설계 분야를 오기위해서 어떻게, 무엇부터 공부를 해야하는지를 여쭤보시더라고요. 이제까지는 "교수님들이 만든 커리큘럼을 참고하면 좋다"라는 식으로 답변을 드렸었는데, 막상 보시면 공부해야할 내용이 방대합니다. 어찌보면 좋은 답변이 아니다 생각이 들어서, 이번시간에는 제가 실제 현업에 와서 유용하게 사용중인 지식들을 바탕으로, 짧지만 굵은 로드맵을 만들어 보았습니다. 오늘 이야기 요약해보면, 장담컨데 로드맵 대로 공부하신다면 현업 설계 엔지니어 중에서 평타 이상 실력은 확보할 수 있다 입니다. 영상으로 함께해요 :) https://youtu.be/qzQFshHQxfI

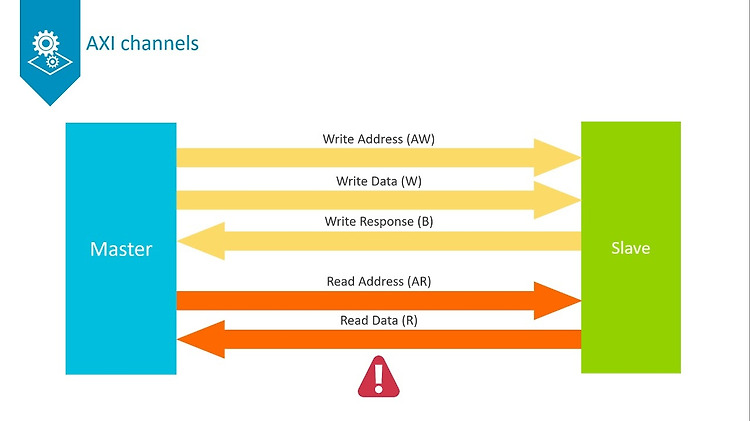

AXI Write bvalid 에 대해서 (완벽하게 목적지에 Data 가 Write 가 되었습니까?)

Introduction AMBA 의 AXI 공부하다보면, Channel 의 개수가 Read 는 2개 Write 는 3개 인 것을 보게 됩니다. Write 는 B Chaanel 이 별도로 존재해서 이고, 왜 Write 는 1개가 더 추가되었지? 의 의문을 해소합니다. Write Channel (노란색 화살표) AW: Write address channel signals W : Write data channel signals B : Write response channel signals 가 존재합니다. B : Write response channel signals B 는 Write Response 로 Write 가 정상적으로 목적지까지 전달이 완료되었는지를 확인하는 채널입니다. BRESP 의 응답 결과를 보..

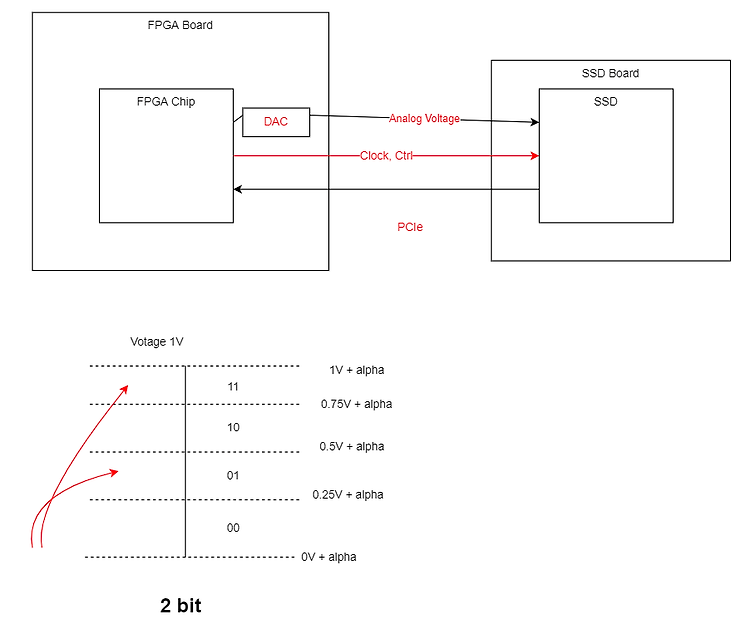

220925 라이브

Q A FPGA board로 SSD 내 memory 소자를 전압단위로 컨트롤 할 수 있을까요? 가능하다면 FPGA로 process-in-memory를 구현할 수 있을까요? 요점은 이를 이용해 deep learning의 weight을 bit 단위로 non-volatile하게 저장할 수 있을거라고 생각해서요 (가능함.) 보류. external -> 중간 그림은 문서 하단 참고 기존 방법 (ex, SATA) 대비 어떤 면에서 효율적인가? PPA (Performance, Power, Area) 제가 PIM을 하는게 아니라 잘 모르지만 아날로그로 데이터도 저장하고 연산도 하는걸로 알고있습니다. 디지털 기반의 연산장치가 아니라요 요즘에 riscv에 관심 생겨서 공부할려합니다. 책 사서 4비트 riscv cpu..

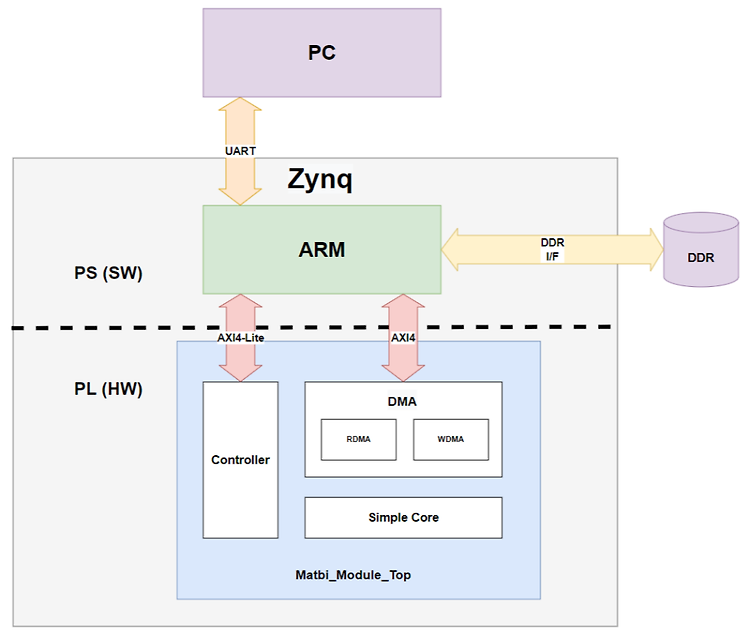

[설계독학] [VerilogHDL, HLS, FPGA를 이용한 AMBA System 1장] 강의계획서 및 소개

안녕하세요. 설계독학맛비입니다. 최근 토요일 오전마다 오프라인 강의를 진행하고 있습니다. 강의 내용의 녹화본을 몇몇 내용을 제하고 영상으로 제작하고 있어요. 해당 강의내용을 바탕으로 Verilog HDL Season2 제작의 Base로 삼을 예정입니다. 해당 내용으로 첫 오프라인 강의라 익숙치 않네요. 제가 말이 꼬이거나 할 순 있는데, 전달하고자 하는 내용은 나름 잘? 담았내려고 노력하고 있습니다. (이해를 부탁... ㅠ.ㅠ) 최종적으로 만들고자 하는 System 은 다음과 같아요. AMBM Bus 중 AXI4 를 이용한 System 을 구축해볼 생각입니다. 해당 System 을 기반으로 정말 다양한 IP 를 설계하고 검증하고 FPGA 에서 동작시켜보는 Full IP 설계를 경험하실 수 있을꺼에요...