반응형

안녕하세요 맛비님!!

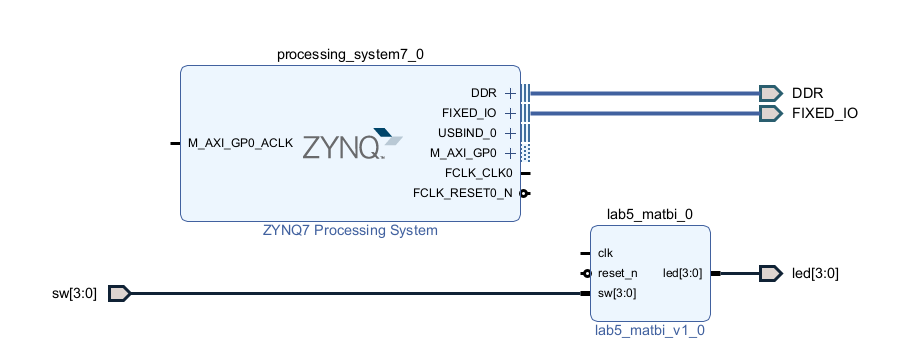

1. 다음 사진처럼, DDR, FIXED I/O, LED가 칩 외부의 보드 핀과 연결되는 것으로 알고 있는데, LED는 출력부분이니까 이해했습니다.

그런데 DDR은 Double Data Rate로, 클럭의 양쪽 엣지를 동기화하여 입력값을 받는다고 알고 있는데 쓰이는 이유가 궁금합니다.

그리고 FIXED I/O는 인터넷에서 찾아보니, Standard I/O 와 연관이 되어있고, Standard I/O 는 LVDS, LVCMOS 등등의 표준 규격으로 알고 있지만, FIXED I/O의 정확한 개념을 잘 모르겠습니다.

(고정된 input output인가요?)

2. Vitis를 사용하지 않고, Vivado에서 바로 open hardware 후 program device를 하지 않는 이유가 궁금합니다!

3. create clock으로 주기를 만들어줄 수 있는것으로 알고있는데, xdc파일 클럭 관련 문법을 안쓰고 zynq ip로 clock부분 활성화 시키는지 궁금합니다!

========================================================

안녕하세요 :)

1. 다음 사진처럼, DDR, FIXED I/O, LED가 칩 외부의 보드 핀과 연결되는 것으로 알고 있는데, LED는 출력부분이니까 이해했습니다.

그런데 DDR은 Double Data Rate로, 클럭의 양쪽 엣지를 동기화하여 입력값을 받는다고 알고 있는데 쓰이는 이유가 궁금합니다.

"DDR 에서 Double data rate 를 사용하는이유" 라고 해석이 되는데, 이 부분은 BW 를 두배로 늘리기 위함입니다. 자세한건 구글링 부탁드립니다.

그리고 FIXED I/O는 인터넷에서 찾아보니, Standard I/O 와 연관이 되어있고, Standard I/O 는 LVDS, LVCMOS 등등의 표준 규격으로 알고 있지만, FIXED I/O의 정확한 개념을 잘 모르겠습니다.

(고정된 input output인가요?)

말그대로 고정된 I/O 입니다.

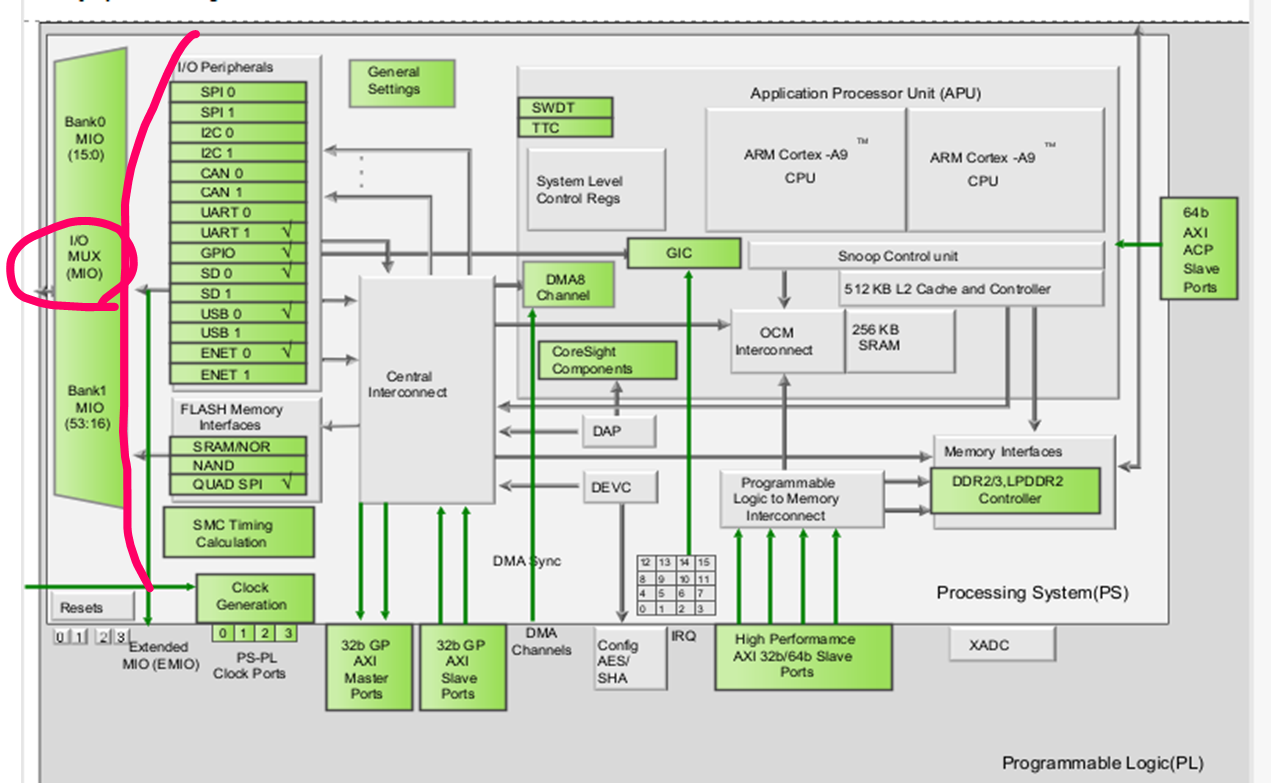

다음 그림처럼 펼쳐서 보면 MIO 가 있습니다.

이 MIO 는 다음 그림을 참고하세요.

2. Vitis를 사용하지 않고, Vivado에서 바로 open hardware 후 program device를 하지 않는 이유가 궁금합니다!

강의의 내용을 더 진행하시다 보면, Vitis 사용합니다. :)

3. create clock으로 주기를 만들어줄 수 있는것으로 알고있는데, xdc파일 클럭 관련 문법을 안쓰고 zynq ip로 clock부분 활성화 시키는지 궁금합니다!

zynq 의 ARM 에서 만들어주는 Clock 을 사용함으로, xdc file 을 통해 명시하지 않아도 됩니다.

외부 오실레이터의 clock 을 입력받아서 사용한다면 알고계신 xdc 파일 클럭 문법을 사용하시면 됩니다.

즐공하세요 :)

반응형

'개발 편의성을 위한 소소한 Tips > 04 질의 응답 정리' 카테고리의 다른 글

| [Verilog HDL Q/A. 028] 왜 F/F들은 clock의 posedge edge에만 동기화 되는거지? posedge 와 negedge 둘 다 동기화될 수도 있지 않을까? 속도도 2배 빠를 것이고, double edge F/F이 있는데? (0) | 2023.01.18 |

|---|---|

| HW 엔지니어가 알아두면 좋을 소소한 알쓸신잡 (0) | 2022.08.16 |

| [Verilog HDL Q/A. 026] DTU와 testbench에 대해 제가 제대로 이해한건지 궁금하여 여쭤봅니다 (0) | 2022.05.22 |

| [FPGA Q/A. 025] timing violation (0) | 2022.04.30 |

| [FPGA Q/A. 024] board off on 시 bitstream 유지 (0) | 2022.03.11 |