|

설계독학에서 진행 중인 쉬어가기의 내용입니다. 모든 글의 저작권은 맛있는비빔밥에게 있습니다. ^^ |

설계독학 유튜브

Intro

안녕하세요. 설계독학의 맛비입니다.

오늘은 쉬어가기의 세번째 시간을 준비해 봤습니다.

바로 HW 설계방식 중, 최신? 이라고 말하기는 좀 그렇지만, 그래도 나름 최신의 설계방법 중 하나인 HLS, High Level Synthesis 에 대해 말씀드리고자 합니다.

HLS 를 사용한지는 3년 정도 되었습니다. HLS 를 아직 다 모르지만, 적응하면 할 수록 도움이 됩니다. 사내 엔지니어 분들은 전부 HLS 를 사용을 하십니다.

Verilog 강의가 끝나면, HLS 에 대해서 말씀드릴 수 있을 것 같아요.

오늘 쉬어가기에서는 내용을 준비하다 보니 방대해서, Part 를 2개로 나눠서 업로드를 해볼 예정입니다.

Part 1 에서는 HLS 란 무엇이고, 어떤 장점이 있는지에 대해서 설명을 드릴꺼구요.

Part 2 에서는 HLS tool 종류 및 HLS 가 사용된 사례에 대해서 소개를 해드리려고 합니다.

오늘은 이런 설계기법이 있구나, 그리고 공부해보면 좋을 것 같다의 동기부여가 되었으면 좋겠습니다.

재밌게 봐주세요. 그럼 시작하겠습니다.

Typical Design Flow

먼저 HLS 가 무엇인가를 말씀드리기 전에, Typical Design Flow 를 간단하게 설명을 드리겠습니다.

오늘 말씀드릴 HW 설계의 Target 은 Logic Synthesis 까지 될 것 같아요.

먼저 Spec 을 정의를 해야합니다. Design 할 모듈의 기능 정의 부터 시작해서, 어떤 Library 를 사용하는가, 그리고 흔히 PPA 라고 부르는 Performance / Power / Area 등등을 예상해보는 단계입니다.

High Level Design 은 전체 System 상에서, 모듈간의 Interface, 흔히 Bus 죠. 연결을 어떻게 할 것인가?

그리고, Processor 와 Core module 간의 Protocol 등.. 을 정의를 합니다.

High Level Design 이 Architecture 라면, Low level design 은 Micro Architecture 라고 생각하시면 될 것 같습니다. Target Spec 에 맞게 좀더 세부적으로, 로직을 얼만큼 사용해서 모듈을 구현할지를 정의해 봅니다.

Low level design 까지 오면, Performance / Area 는 90% 수준? 으로 예상이 가능합니다.

그 다음 RTL Coding 을 하게 됩니다. 이 RTL Coding 이 바로 여러분들이 현재 배우고 있는 Verilog HDL 입니다.

이 Flow 에서 아실 수 있듯이, RTL coding 은 모든 Spec 과 상세한 문서가 정리가 된 다음 이루어지는 작업입니다.

제가 일을 배울때에도 제 예전 사수분이 항상 말씀하시는게 문서 인데, 결국 RTL Coding 보다 중요한게 문서라고 생각이 듭니다.

Verilog HDL 은 하나의 Language 이고 이는 다른 설계기법으로 대체가 가능합니다.

그 새로운 설계기법이 바로 오늘 말씀드릴 HLS 입니다.

Flow 를 조금더 살펴보면 RTL Coding 이 완료가 되면, Functional Verification 을 하게 됩니다. RTL 이 spec 에서 요구하는 Function 과 정확하게 Match 하는지 확인해야합니다.

그 다음 Logic Synthesis 를 통해서 RTL coding 을 실제 사용할 Library 를 기반으로 회로를 만들어 냅니다.

그 뒤로 많은 Flow 가 있구요. 이는 많은 Engineer 와 Cost 을 요구합니다.

그래서 반도체 칩이 나오는 과정이 돈이 많이들고, 진입장벽이 높다 라는 생각을 갖게하는 이유이죠.

HLS Flow

자 그럼, HLS 는 무엇인지 말씀 드리겠습니다.

HLS 는 High Level Synthesis 의 약어로, C / C++ / System C 와 같은 High level 의 Language 를 사용하여, RTL Coding 과 검증을 하는 것입니다.

Verilog HDL 보다 상위 언어인 C 를 예로 들면, C 로 설계시, HLS Tool 이 RTL Language 인 Verilog HDL 혹은 VHDL 로 Generation 을 해줍니다.

기존에는 Verilog HDL 로 RTL coding 하고 Function 검증 했다면, HLS 는 RTL Generation 이 가능하기 때문에 C++ 로 설계 및 검증을 할 수 있습니다.

위 Flow 에서, 다음과 같이 HLS Coding Flow 가 추가가 되면 됩니다.

여기서 RTL Coding 의 전부를 HLS Flow 로 대체할 수 없기때문에 HLS Flow 를 RTL Coding 전에 배치를 했습니다.

기존의 해야되는 업무인 Spec 과 Architecture 를 정의하는 일은 변함이 없습니다. 단지 HLS Flow 가 추가 되었습니다.

Verilog 대신에, C 로 설계를 하는데, Flow 만 늘고 공부해야할 내용이 추가가 되었습니다. 당연히도 HLS 는 공부를 해야 사용할 수 있습니다.

그러면 우리가 왜!! HLS 를 공부해야 되는가.. 에 대해서 설명드리기 위해서, 장점과 단점에 대해 설명을 드리겠습니다.

HLS 의 장단점

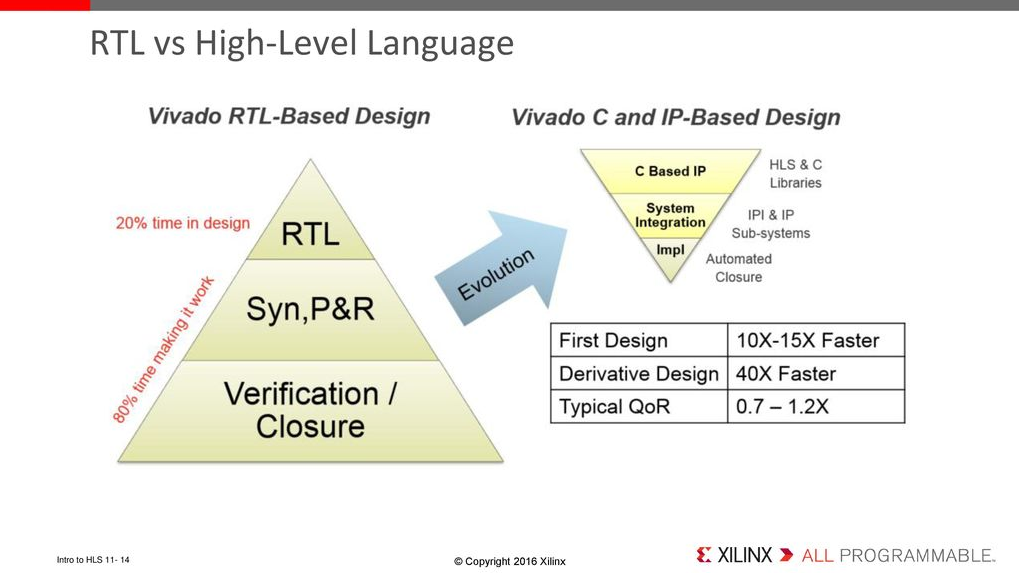

오늘은 FPGA 기반인 Xilinx 사의 Vivado HLS 를 기준으로 설명을 드리겠습니다.

다음 그림에 장단점이 나와있습니다.

장점

장점 Time, 즉 시간을 단축 시킬 수 있습니다. 이게 다입니다.

시간을 줄인다는건 첫번째로 필요한 man power 를 줄일 수 있습니다. 곧 돈을 줄이는 과정입니다. 그리고 Time to market 에 엄청난 이득을 불러 올 수 있습니다.

먼저 출시한다는 것은 돈을 벌 기회가 늘어난다는 것이죠.

제가 HLS 를 공부하고 사용하는 이유는 돈을 줄이고, 돈을 벌 수 있기 때문입니다.

그럼 어떻게 시간을 줄일 수 있는지 살펴보겠습니다.

기존의 FPGA 상에서 RTL 설계의 Coding 은 큰 이슈가 아닙니다. 전체 개발시간의 20% 밖에 안되죠. 문제는 합성과, PnR 과정 그리고 검증과 Timing Closure 입니다.

전체의 80% 를 차지하는 과정이고, 어렵고 복잡한 Design 일수록 이 부분의 portion 이 90% 이상이 될 수 있습니다.

그런데, HLS 를 통한 설계가 되면, Coding 과 검증시간이 단축됩니다. 문서상에는 2~5 배 가량 빠르다 라고 하는데, 제 경험상 조미료 조금 쳐서 평균적으로 3배의 설계 및 검증시간 이득이 있다라고 생각을 합니다.

고수는 전통적인 Verilog HDL 의 설계가 HLS 대비 더 빠르고 정확할 수 있습니다. 3배라고 말씀드린거는 저같은 10년차 엔지니어 기준입니다.

그 이유의 첫번째로,

- Simulation Time 을 들 수 있습니다.

기존의 Coding 은 Verilog 그리고 검증은 System Verilog 를 이용해서 Functional 검증을 합니다.

여기서, RTL Code 를 이용해서 Function simulation 을 돌린다.. 라는 말자체가 굉장히 많은 시간을 소모하게 됩니다.

Verilog 를 이용한 simulation 이죠. HLS 는 설계도 C 로 하지만, Function 검증 또한 C 로 합니다.

우리가 알고있는 컴파일러로 C 를 빌드하여 실행파일을 만들고, 실행하면 됩니다. 여기서 Simulation time 만 20배 정도 차이가 납니다. (제 경험상 입니다.) - 두번째로는 Coding 시간 단축입니다.

설계를 Verilog 하고, 검증 코드 또한 Verilog 작업이 들어가야합니다.

HLS 의 설계 언어는 C 입니다. 검증또한 C 입니다. 코딩해야할 line 수 자체가 여기서 이미 10배이상 차이가 납니다.

그리고 가독성 또한 차이가 있죠.

Coding 시간을 줄여준다는 말은 Code line 수가 적다는 뜻이고, 이는 곧 Debugging 해야할 부분이 적어집니다.

그리고 Coding 시간이 줄었기 때문에 기회가 되면 다양한 Architecture 를 Try 해볼 수 있습니다.

결론적으로 이 부분에서도 10 배정도의 이득을 볼 수 있습니다. - 세번째로는 Timing Closure 입니다.

FPGA 를 해보신 분은 아시겠지만, High frequency 의 Clock 을 사용한다면 Timing closure 가 굉장히 어렵고 시간이 오래걸리는 이슈임을 아시고 있을 거에요.

여기서 Timing closure 를 간략하게 설명드리면, 원하는 Clock Frequency 에 Core 를 동작시킬 수 있도록 Implementation 하는 것을 말합니다.

예를들어, 300 MHz 에 Core 를 돌리고 싶다. (FPGA 에서 꽤 높은 frequency 입니다.) 그런데 RTL 설계에서, 300 MHz 를 돌릴 수 없도록 Human 이 코딩을 했습니다.

그럼 300 MHz 를 돌릴 수 있도록 Verilog HDL 을 수정해야하고, 검증하고, FPGA Implementation 을 해야합니다.

말로하는데도 빡세네요..

하지만 HLS 는 C 에서 Verilog Code 를 Generation 합니다. Generation 과정에서 Library 정보와 Target Frequency 정보가 같이들어가고, 이는 해당 frequency 에 동작할 수 있는 RTL Code 가 Generation 됩니다.=

5 배정도의 시간 이득이 있다 생각합니다.

단점

단점은 무엇일까요. 단점은

첫번째로

- HLS 를 공부해야합니다. 새로운 Flow 가 추가가 되었습니다. 모르면 쓸 수 없죠.

하지만 HW 설계 경험을 쌓았고, C 를 해보신 분이라면 금방 익히고 잘쓰는 모습을 봐 왔습니다.

이는 노력에 따라 큰 단점은 아니겠죠. - 두번째 단점은 QoR 입니다.

C++ → RTL 을 Generation 한다고 했습니다. Hand RTL 을 사람이 직접 코딩한 RTL 이라고 하겠습니다.

여기서 Generated RTL 이 실제 FPGA 의 Util Resource 관점에서 Hand RTL 보다 크게 사용할 수 있습니다.

그런데 여기서 무조건 Hand RTL 보다 QoR 이 나쁘냐? 그건 또 아닙니다. Flow 에서 정의한 Spec 과 Architecture 를 정확하게 이해하고, HLS 또한 정확하게 이해한다는 가정이면

Hand RTL 보다 더 좋은 QoR 을 낼 수 있습니다.

즉, 단점은 극복이 가능한 부분입니다. 장점은 기존의 방식으로는 극복하기 어려운 부분이었구요.

마무리

오늘 설명드린 내용을 정리하고 마무리 하겠습니다.

HLS 가 무엇이고, HLS 를 사용함으로써의 장단점에 대해 알아보았습니다.

장점은 시간을 절약할 수 있습니다.

단점은 HLS 와 Spec 에 대한 정확한 이해가 없다면 QoR 이 떨어질 수 있습니다.

지극히 제 경험과 문서를 바탕으로 정리했습니다. 여러분들의 생각은 어떠신가요?

다음시간에는 쉬어가기의 연장선으로 HLS tool 종류 및 사용 사례에 대해서 말씀을 드리겠습니다.

그럼 다음시간에 봬요~

'설계독학맛비 YouTube > 00 쉬어가기' 카테고리의 다른 글

| [설계독학] [쉬어가기 5장] 비메모리 설계를 위한 커리큘럼?? 커리어 패스?? 지식?? (정답은 없습니다 ^^) (11) | 2020.12.22 |

|---|---|

| [설계독학] [쉬어가기 4장] 새로운 설계방법론 HLS 의 Tool 종류와 성공사례 (0) | 2020.12.14 |

| [설계독학] [쉬어가기 2장] AI Inference Accelerator 의 승자는 누구일까? GPU, NPU, FPGA 의 현주소를 알아보자. (0) | 2020.12.14 |

| [설계독학] [쉬어가기 1장] 비메모리 설계를 배우면 할 수 있는 일!! (0) | 2020.12.14 |

| Matbi's 쉬어가기 History (4) | 2020.12.12 |