설계독학맛비 YouTube

220626 라이브

반갑습니다! 오랜만에 뵙습니다 :) 1 RNN이나 LSTM 등 다른 아키텍처도 궁긍해요. IEEE 논문에 올라온 내용을 보고 다른 아키텍처 구현은 어려울까요? 어렵긴 하지만 되지 않을까…? 2 Vivado FPGA implementation시, Timing Path중에 Intra timing path와 Inter timing path가 있던데 그 두개가 무엇인지, 어떤 차이가 있는지 알려주시면 감사하겠습니다. intra timing path : 동일 Clock 내의 path inter timing path : 서로다른 Clock 에서의 path 3 Zynq SoCs과 ACAPs의 차이점은 무엇인가요? ACAPs 최신이라 Util, Perf 4 Zynq SoC 플랫폼에서도 Vitis AI를 사용할 수..

[설계독학] AI HW 강의를 Open 했습니다!!

안녕하세요. 설계독학맛비입니다. 오랜만의 공지글로 인사드립니다 :) 금일 (22/06/16) 에 맛비유니버스 세번째 강의인 "AI HW" 강의가 Open 되었습니다. (만드는데 정말 오래걸렸..... 컥;;;) 한달간 30% 할인을 진행중이니, 함께하실 분들은 같이 하셨으면 좋겠습니다. 인프런에서 "AI HW" 검색하시면 됩니다. 이후로는 쉬어가기의 일환으로 강의가 아닌 여러분들에게 도움이 될만한 내용들로 영상을 만들어서 업로드할 예정입니다. 다시 만나뵙게되어서 반갑습니다~ 같이 즐공해보아요 :) https://www.inflearn.com/course/실전-하드웨어-설계?inst=818f0eee 설계독학맛비's 실전 AI HW 설계를 위한 바이블, CNN 연산 완전정복 (Verilog HDL + FPG..

210903 라이브

Q A 저는 지금 26살 이며, 하드웨어회로랑 기구설계를 하고있습니다. 시스템반도체 쪽으로 예전부터 공부 및 자리 잡고 싶었다. 막상 이직하려니 그쪽 경험 및 지식이 부족해서 방향을 시스템반도체쪽으로 전향하고 싶은대 조언 좀 부탁드려도될까요? 시스템 반도체 분야에서 필요한 지식, 경험 디지털 회로 설계 → ASIC, FPGA 수행 시 필요한 것들. HW 지식 (학교에서 배우는 지식이 굉장히 쓸모 있습니다.) 디지털설계회로, + 실습 SoC 설계 컴퓨터 구조. Verilog HDL or VHDL 어떤 모듈이 있을 때, 설계가 가능한 수준. 제가 이직의 보장, Verilog HDL 책 1독 (지식) VERILOG HDL 디지털 설계와 합성의 길잡이 책에서 설명하는 내용을 이해하기. 경험이 없는 상태.. → ..

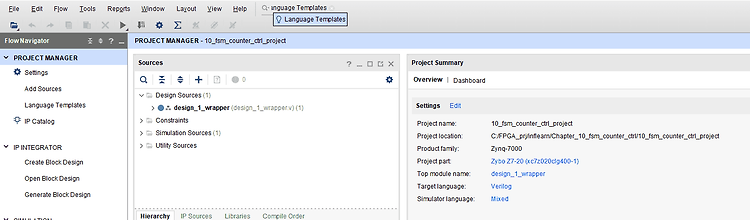

Xilinx Vivado bram 쉽게 !!! 생성 하기.

지금은 아주 쉽게, Xilinx 의 BRAM 을 생성 및 Test 할 수 있어요! 쉽게! 라는 취지 이기 때문에 바로 본문 들어가겠습니다. 아주 간단하게 Test 해봤습니다. 1. 프로젝트를 하나 만듭니다. 2. 그 상태에서 위의 돋보기에 "Language Templates" 이라고 검색해서 눌러주세요 3. Veriog -> Synthesis Constructs -> Example Modules -> RAM -> BlockRAM -> 원하시는 메모리 코드 선택 4. template code 메모리를 .v 코드로 복 붙 했습니다. 5. synthesis 눌렀습니다. 6. 결과 확인 BRAM 0.5 로 resource 잡히신거 보이시나요? 잘돼요 ㅎ 참고로 implementation 을 통한 bitstrea..

210822 라이브 방송

오늘의 주제 QA Q A 1 다름이 아니라 제가 디지털 회로 설계 쪽으로 진로를 정했는데, 한국에 디지털 설계 관련 해서 스타트업밀고 큰회사가 있는지를 잘 모르겠어서 질문을 드리고 싶습니다 ㅠ 얼마전에 진로상담을 했었는데 한국기업은 많이 없다고 들었어서요 ㅠ 맛비님은 상황을 잘 아시다보니 이렇게 메일로 도움을 받고싶어 연락을 드립니다 ㅠ 디지털 설계 대기업.. 엄청 많은데. 대기업 삼성전자 LG 전자 LG 디스플레이 삼성 디스플레이 방산, 테크윈 현대 오트론! 외국계 (설계 , 지원 FAE, 돈은...) 시놉시스 케이던스 멘토 (지멘스) 중견기업 텔레칩스 (Top) 칩스앤미디어 실리콘웍스 고영테크놀로지 넥스트칩 (ncn) 어보브 반도체 제주반도체 리버트론 교육, 용역 메이플전자 라닉스 에이디테크놀로지 동..

210613 라방 QnA

오늘 불시 라방도 함께해주셔서 감사합니다 :) Q A 1 언어는 vhdl쓰고요 독학점 할라는데 보드를 구매해서 하는게 나을지 고민입니다 ㅜ 디지털 회로설계를 하신다 + 통신, 회사업무 + 이직, 혹시 어떤 업무 하실까요? 원하시는 목표? (공부의 목표?!) 이직을 생각한다고 하시면, 사용하는 회사 VHDL < Verilog HDL FPGA 보드 구매는 추천드려요. (수입이 있다.) 30만원은 2 ai가 부상하면서 디지털 회로 설계자도 많이 필요해졌다고 들었는데, ai관련 회로는 대부분 디지털회로로 만들어지는 건가요? 제가 아예 모르는데 왜 그런지 간단히 설명해주실 수 있나요? 디지털회로가 아니면, 반대개념, 아날로그 회로 디지털회로로 만들어진다. (대부분) 디지털회로 vs 아날로그 회로 디지털회로 :..

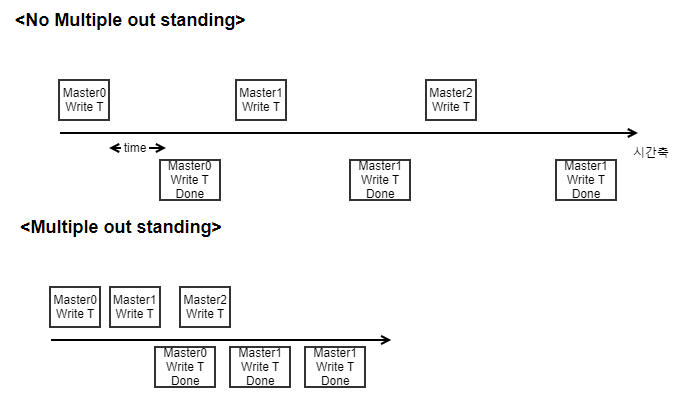

210522 라방 QnA

QnA 입니다. 기습 라방에 참여해주셔서 감사합니다. 즐공입니다. :) Q A 1 vhdl이 더 정확하게 설계할 수 있다 이 부분은 저도 잘 모르겠습니다. ㅠ 2 Vivado GUI 에서 IP 들 make external 하는게 있고 안하는게 있던데 어떤 차이인가요? 28:00 부터 시청 (영상 참고) 3 multiple outstanding 53:00 부터 시청 (영상 참고) Bus Performance 향상에 사용할 수 있는 concept. 4 xsa 파일을 형성 Vivado 에서 Zynq 가 아니더라도, FPGA Chip (Vertex, ultrascale...?) 영상을 참고하시면 됩니다. 5 xdc 파일 보드 의 Pin map 설정, master.xdc timing, clock, pnr (chi..

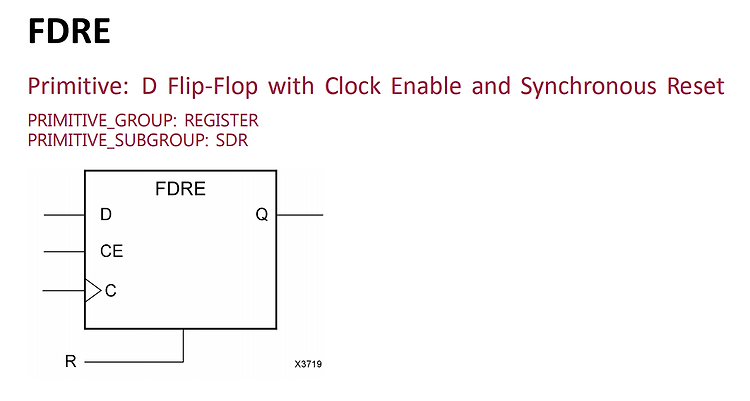

Xilinx FPGA Reset Guide

안녕하세요. 맛비입니다. Xilinx FPGA 사용시 Reset 의 Coding Guide 입니다. (출처는 Xilinx 의 공식 교육자료에 있는데.. 어딨는지는 기억이) 제가 문장에서 "피하라고" 라는 문장을 사용한 이유는.....! 사용해도 동작 합니다. 하지만 굳이 사용할 필요는 없기 때문입니다. 1.F/F 에서 set 과 reset 을 둘다 사용하는 것을 피하세요. -> 추가적인 LUT 를 사용하게 됩니다. (F/F primitive cell 은 하나만 지원합니다.) always @ (posedge clk, posedge set, posedge reset) begin if(reset) a_reg