분류 전체보기

210613 라방 QnA

오늘 불시 라방도 함께해주셔서 감사합니다 :) Q A 1 언어는 vhdl쓰고요 독학점 할라는데 보드를 구매해서 하는게 나을지 고민입니다 ㅜ 디지털 회로설계를 하신다 + 통신, 회사업무 + 이직, 혹시 어떤 업무 하실까요? 원하시는 목표? (공부의 목표?!) 이직을 생각한다고 하시면, 사용하는 회사 VHDL < Verilog HDL FPGA 보드 구매는 추천드려요. (수입이 있다.) 30만원은 2 ai가 부상하면서 디지털 회로 설계자도 많이 필요해졌다고 들었는데, ai관련 회로는 대부분 디지털회로로 만들어지는 건가요? 제가 아예 모르는데 왜 그런지 간단히 설명해주실 수 있나요? 디지털회로가 아니면, 반대개념, 아날로그 회로 디지털회로로 만들어진다. (대부분) 디지털회로 vs 아날로그 회로 디지털회로 :..

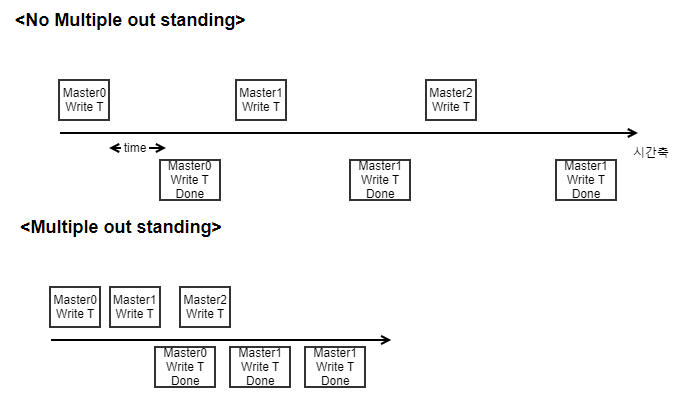

210522 라방 QnA

QnA 입니다. 기습 라방에 참여해주셔서 감사합니다. 즐공입니다. :) Q A 1 vhdl이 더 정확하게 설계할 수 있다 이 부분은 저도 잘 모르겠습니다. ㅠ 2 Vivado GUI 에서 IP 들 make external 하는게 있고 안하는게 있던데 어떤 차이인가요? 28:00 부터 시청 (영상 참고) 3 multiple outstanding 53:00 부터 시청 (영상 참고) Bus Performance 향상에 사용할 수 있는 concept. 4 xsa 파일을 형성 Vivado 에서 Zynq 가 아니더라도, FPGA Chip (Vertex, ultrascale...?) 영상을 참고하시면 됩니다. 5 xdc 파일 보드 의 Pin map 설정, master.xdc timing, clock, pnr (chi..

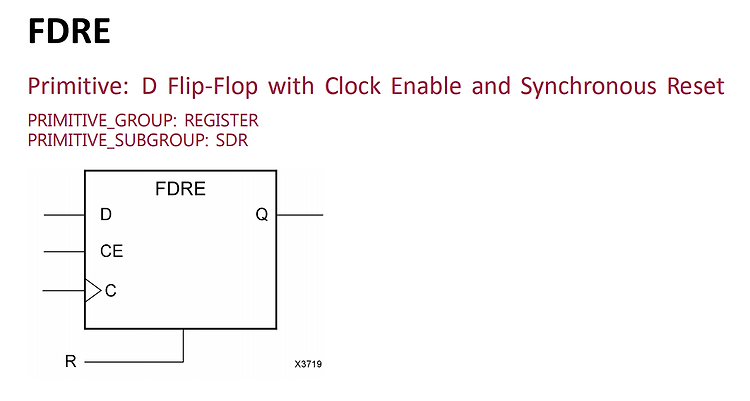

Xilinx FPGA Reset Guide

안녕하세요. 맛비입니다. Xilinx FPGA 사용시 Reset 의 Coding Guide 입니다. (출처는 Xilinx 의 공식 교육자료에 있는데.. 어딨는지는 기억이) 제가 문장에서 "피하라고" 라는 문장을 사용한 이유는.....! 사용해도 동작 합니다. 하지만 굳이 사용할 필요는 없기 때문입니다. 1.F/F 에서 set 과 reset 을 둘다 사용하는 것을 피하세요. -> 추가적인 LUT 를 사용하게 됩니다. (F/F primitive cell 은 하나만 지원합니다.) always @ (posedge clk, posedge set, posedge reset) begin if(reset) a_reg

210425_라이브방송_QnA

Q A rtl로 짠거랑 c로 짠거랑 같이 쓸려고하는 별로인가요? 저는 이렇게 쓰고 있다. c로 짠거 == HLS HLS → RTL RTL + RTL 징크도 좋지만 스파르탄같은 저가 fpga로 하는게 낫은경우도 있을것 같아서요.. 가격의 이슈.. Zynq > spartan 교육용 Zynq 다루기에는 징크가 훨씬 쉬운것 같네요.. 이거는 잘 모르겠어요. zynq 를 처음배우시고 → 다른 FPGA FPGA의 DRAM도 사용하시나요? FPGA 안에 DRAM 은 없고. HBM (High bandwidth memory) FPGA ↔ DRAM DRAM 잘 사용해요. PL에서 DRAM에 데이터를 R/W 해보고 싶은데, 어떤 방식을 이용할수있을까요? AXI 를 아셔야 되요. 혹시 영상같은것은 타입이 주로 RGB24로..

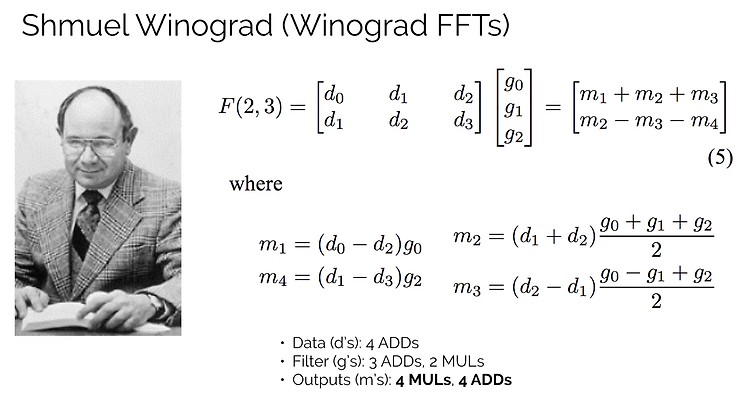

Fast Algorithms for Convolutional Neural Networks

논문 링크 : arxiv.org/abs/1509.09308 영삼 참고 : www.youtube.com/watch?v=j4CIomZfsdM youtu.be/Xh2hBMUYKAE 논문 년도 : Nov 2015 (CVPR 2016) benchmark : github.com/soumith/convnet-benchmarks 오래된? 논문이긴 한데, 첫 제품이 나온 시점에서 연산 최적화를 해볼 수 있는 아이디어를 조사합니다. Abstract Winograd’s minimal filtering algorithms 을 사용하여 CNN 을위한 새로운 종류의 빠른 알고리즘을 소개합니다. 실제 적용이 되기 위해서 Operation speed 가 중요한데, 이를 위해서 Winograd Convolution 을 사용합니다. W..

CNN (Convolution Neural Network) 연산에 대해 이해해보자. (CNN Explainer)

안녕하세요. 맛비입니다. 오늘은 AI HW 에서 보편적으로 널리 사용되는 연산 중 하나인 CNN (Convolution Neural Network) 을 쉽게 이해할 수 있는 Tool 을 소개해 드리려고 합니다. CNN 연산을 처음 접했을 때, 헷갈리는 부분들이 있었는데요. (2D Convolution 의 확장판..?) 제가 이해하려고 노력했을때도 헷갈린데, 남에게 설명하는건 더 어렵겠죠. 좋은 자료를 찾은 것 같아서 공유드립니다. 바로 CNN Explainer 입니다. poloclub.github.io/cnn-explainer/ CNN Explainer An interactive visualization system designed to help non-experts learn about Convolut..

2021/02/06 첫번째.. 방송

주먹구구식 방송에도 봐주셔서 감사합니다. 유튜브 링크입니다. youtu.be/FcwG7FRh8OU 다음은 제가 두뇌 필터링을 거치지 않고, 막.. 적은 내용입니다.. Question Answer 현업에서 verification도 verilog로 하시나요? system verilog를 공부해야 하나 고민이네요 Verification 간단한거는 Verilog 쓰고 있구요. System Verilog 는 검증엔지니어는 필수! verilog로 할수도 있고 systemverilog에서 UVM이용해서 할수도 있고 formal verification하셔도 되죠. 다른 언어로 하고 싶으시다면 python이랑 cocotb 써서 하셔도 됩니다. 이게.... 음 Core 설계 할때, HLS 를 사용해요. HLS 특징. ..

[AI-Based Super Resolution HW IP] Deepfield-SR 을 소개합니다.

안녕하세요. 맛비입니다. 제가 약간의? 개발 지분을 가지고 있는 제품을 소개하려고 합니다. HW 관련 기술적인 내용은 설계독학유튜브에서도 다룰 예정입니다. 오늘은 기술 이야기는 빼고 가벼운 마음으로 적습니다. 세부적인 내용이 궁금하시다면?! 사장님이 직접 작성하신, 원문은 다음 링크를 참고하셔요. 자세하고 알찬 정보가 있습니다. https://www.notion.so/DeepField-SR-AI-based-Super-Resolution-Accelerated-by-FPGA-21bc7d177d6f47cb8eae194c8e1af2f8 뭐하는 제품 일까요?? 저화질 영상을 고화질 영상으로 바꿔주는 겁니다. Upscale 이라고 합니다. 기존의 Upscale 알고리즘으로는 Bicubic 이 대표적이죠. AI..