분류 전체보기

알아두면 좋을 영상처리 용어 (Video Codec 혹은 영상 관련 업무를 한다면 도움이 될만한 용어들)

영상관련 업무를 하다보면 모르는 용어들이 들리는데요. 알아두시면 도움이 되실꺼에요 :) AAchromatic 색상이 없음. 색상이 없다는 것은 검정색에서 흰색의 범위에 해당하는 회색을 의미한다. Adaptive algorithm(적응적 알고리즘) 어떤 자료를 그 자료에 대한 사전 지식없이 처리하는 알고리즘. Additive color(부가적 컬러) 서로 다른 주파수 분포를 가지는 빛의 조합으로 생성되는 색상. 기본색상은 빨강, 녹색, 파랑이다. 부가 시스템은 방사성이므로 빛을 생성한다. Affine Transform(어파인 변환) 회전, 전이, 크기 변화와 이들의 조합으로 이루어지는 선형 기하 변환. Algorithm(알고리즘) 어떤 문제를 해결하거나 작업을 수행하기 위한 단계들의 집합. Aliasing..

NAND 관련된 회사에 입사할때 알아두면 좋을 cheat sheet

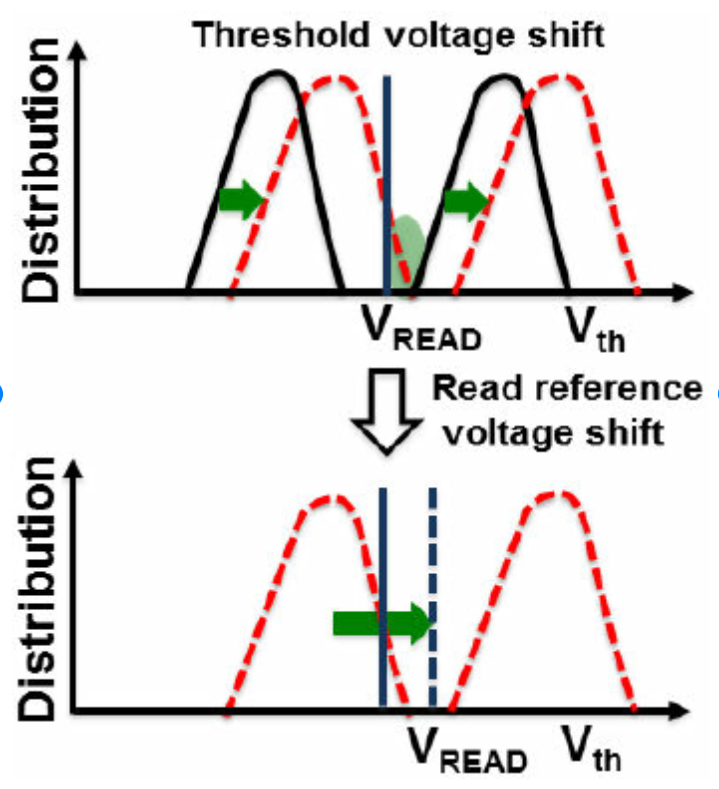

Introduction 국내에 NAND 를 다루는 회사는...? 정말 손에 꼽을 겁니다. 그 회사에서 필요한 지식을 정리합니다. 이정도 내용을 알고있으면 좋겠다...로 받아들이셔야지, 이것을 외우면 100% 합격한다 는 보장하지 않습니다. 썰을 하자면.. 이 내용을 바탕으로 최종면접까지는 갔던...? 기억이 날..듯? 말듯..? 본문 NAND Flash 관련 nand flash slc / mlc / tlc / qlc (Single Level Cell / Multi / Triple / quad) http://www.bloter.net/archives/230738 반도체 공정의 미세화에 따라 비트 에러율이 증가하는 낸드 플래시 메모리에서 고성능 에러 정정 방법은 필수적이다. Low-density parity..

ASIC IP 설계시, 합성 library 의 선택과 Memory library 사용여부

Introduction ASIC 용 IP 를 설계할때, 합성 library 선택과 Mem Library 선택 여부가 중요합니다. Target nm 공정내에 다양한 library 가 존재하며, 이를 선택하는 방법에 대해 고민해봅니다. 합성 library 선택 Target library 내에 세부적으로 hvt 가 있고 svt가 있습니다. 의미는 high voltage threshold (hvt) 이고 standard voltage threshold (svt) 입니다. 물론 lvt( low) 도 존재하고요. lvt의 의미는 낮은 전압 경계를 갖는다는 의미입니다. 즉 쉽게 0,1 스위칭을 할 수 있다는 뜻이되고 이는, 고속 스위칭이기 때문에 전력소모가 심합니다. 그렇기 때문에 IP를 판매하는 업체에서는 libr..

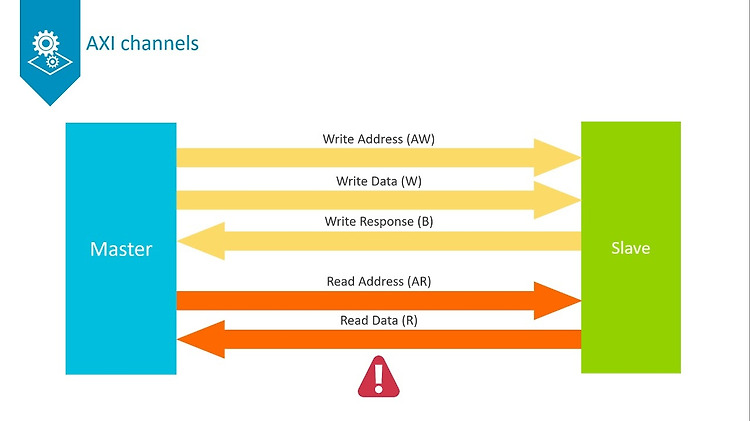

AXI Write bvalid 에 대해서 (완벽하게 목적지에 Data 가 Write 가 되었습니까?)

Introduction AMBA 의 AXI 공부하다보면, Channel 의 개수가 Read 는 2개 Write 는 3개 인 것을 보게 됩니다. Write 는 B Chaanel 이 별도로 존재해서 이고, 왜 Write 는 1개가 더 추가되었지? 의 의문을 해소합니다. Write Channel (노란색 화살표) AW: Write address channel signals W : Write data channel signals B : Write response channel signals 가 존재합니다. B : Write response channel signals B 는 Write Response 로 Write 가 정상적으로 목적지까지 전달이 완료되었는지를 확인하는 채널입니다. BRESP 의 응답 결과를 보..

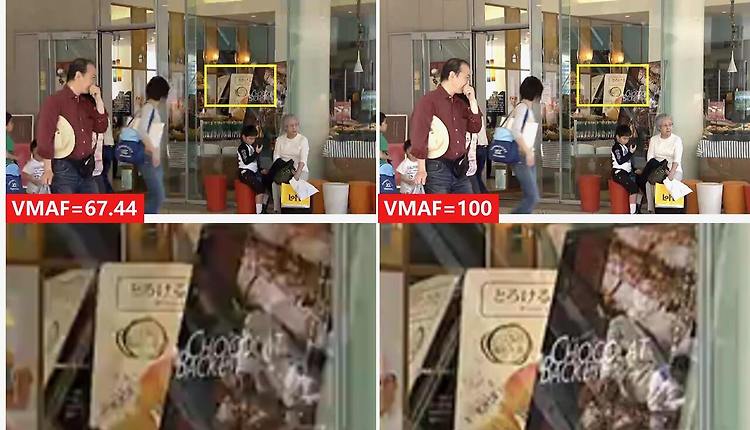

VMAF (Video Multi-Method Assessment Fusion)

VMAF는 Netflix에서 개발한 video quality assessment algorithm 입니다. 압축된 Video (Distorted Video) 와 원본 Video 간의 Visual Quality 유사율의 점수를 내는 방법 중 하나입니다. VMAF 의 점수가 높으면 원본과, 압축된 Video 사이의 Visual Loss 가 거의 없다 할 수 있습니다. (눈으로 보았을때 원본과 차이가 없다.) 기존의 VMAF 처럼 화질 측정 metric 으로 사용하던 유명한 알고리즘으로는 PSNR, SSIM 등이 있습니다. VMAF 의 가장 큰 장점은 기존 Metric 대비 사람이 느끼는 Quality 경험과 유사한 Score 를 내주는 것에 있습니다. OTT 영상을 보다보면 Netflix 의 화질이 다른 O..

1. 영상처리 및 Codec 을 위한 YUV File 및 Video Download site

Introduction FFMPEG 관련 실습 및 Video 공부를 위해서 YUV File 과 Video Bitstream 을 Download 받는 링크를 정리합니다. 실제 주요하게 사용했던 Dataset 들을 정리합니다. 해당 page 는 계속 업데이트 될 예정입니다. 다음 link 의 Video 는 상업이용시 문제가 될 여지가 있음으로 공부용으로만 사용합니다. :) UGC Dataset Youtube 에서는 Video 압축 및 화질측정 분야 연구를 위해서 Data 를 Open 하였습니다. 사실 이거만 받아도 정말 많은 영상 Data 를 확보할 수 있습니다. RAW (날것의, 원본) Data 부터 Youtube 에서 권장하는 Spec 에 맞는 압축된 Data 를 같이 구할 수 있습니다. Codec 뿐만..

220925 라이브

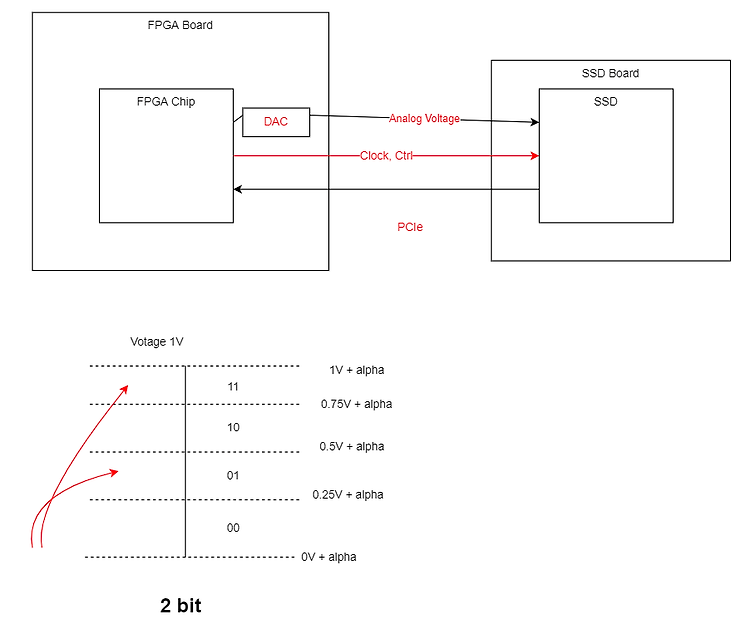

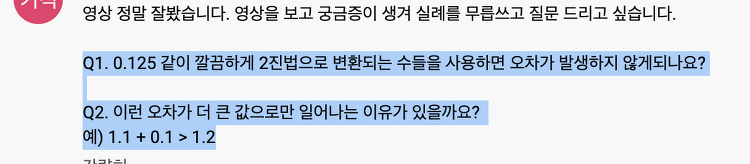

Q A FPGA board로 SSD 내 memory 소자를 전압단위로 컨트롤 할 수 있을까요? 가능하다면 FPGA로 process-in-memory를 구현할 수 있을까요? 요점은 이를 이용해 deep learning의 weight을 bit 단위로 non-volatile하게 저장할 수 있을거라고 생각해서요 (가능함.) 보류. external -> 중간 그림은 문서 하단 참고 기존 방법 (ex, SATA) 대비 어떤 면에서 효율적인가? PPA (Performance, Power, Area) 제가 PIM을 하는게 아니라 잘 모르지만 아날로그로 데이터도 저장하고 연산도 하는걸로 알고있습니다. 디지털 기반의 연산장치가 아니라요 요즘에 riscv에 관심 생겨서 공부할려합니다. 책 사서 4비트 riscv cpu..

HW 엔지니어가 알아두면 좋을 소소한 알쓸신잡

안녕하세요. 설계독학맛비입니다. 최근에 이것저것? 인터넷을 끄적이다가, Hardware Engineer 가 알아두면 좋은 내용들이 있어서 소개해 드립니다. 첫번째 이야기!! 이중 for 문에서 memory index 접근 방법에 따른 Performance 차이. (시간복잡도) 블라인드 앱에서 본 글인데요. 여러분들 맞출 수 있나요? (저도 어버버 할듯... ㅎㅎ) Q. 원문============= 인터뷰 보는데.. 시건복잡도 문제를 수기로 작성해주고 어떤게 더 빠른지 말해달라고 했었는데… 1. 이중 for문 (i -> j 순서) > sum += arr[i][j] 2. 이중 for문 (j -> i 순서) > sum += arr[i][j] 어떤게 더 빠른지 말하라고 했는데.. 혼이 씌었는지 1번이 더 빠르다..